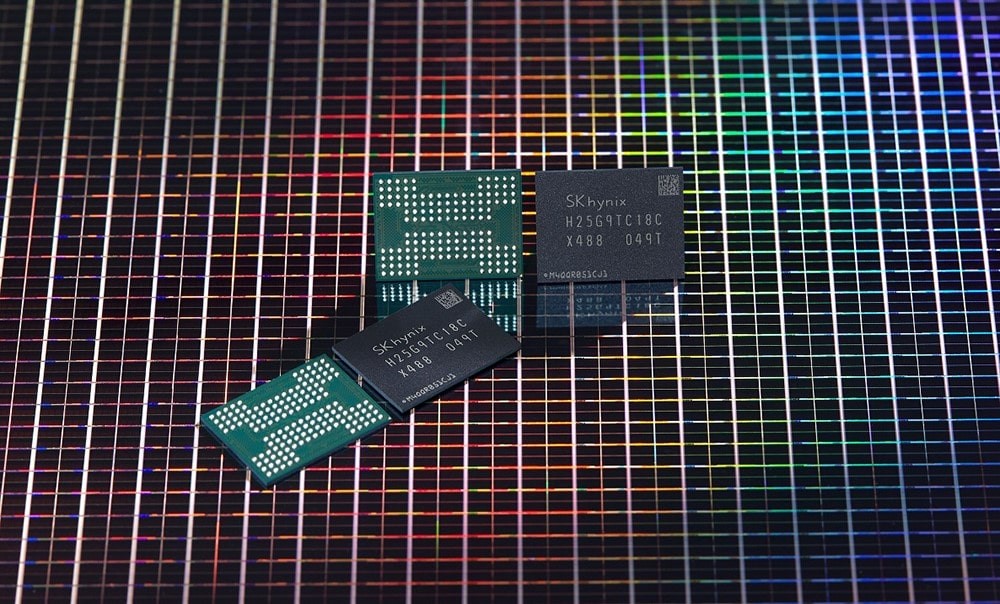

SK hynix Inc اعلام کرد که توسعه بزرگترین حافظه 4D NAND Flash با TLC (Triple-Level Cell) که ظرفیت آن 512 گیگابایت است را به پایان رسانده است. در همین راستا این شرکت نمونه راه حل محصولات را تولید و در اختیار شرکتهای کنترل کننده قرار داد.

SK hynix فناوری 4D را نسبت به محصولات NAND Flash با 96 لایه که ترکیبی از CTF (Charge Trap Flash) با فناوری PUC (Peri Under Cell) کاملا یکپارچه هستند، ارتقا داده است.

حافظه جدید، NAND Flash با 176 لایه نسل سوم محصول 4D است که بهترین تعداد تراشه در هر wafer را برای صنایع تضمین میکند. این امر باعث میشود تا بهرهوری بیت با رقابت پذیری متفاوت هزینه، 35 درصد در مقایسه با نسل قبلی بهبود یابد. با استفاده از فناوری آرایه سلول دو بخشی سرعت خواندن سلول، 20 درصد نسبت به نسل قبلی افزایش یافته است. سرعت انتقال داده نیز با افزایش سرعت فناوری بدون افزایش تعداد پردازشها، با 33٪ بهبود به 1.6 گیگابیت بر ثانیه رسیده است.

با ارائه راه حلهای مورد نیاز محصولات موبایل حداکثر سرعت خواندن به 70٪ و حداکثر سرعت نوشتن به 35٪ بهبود یافته است، SK hynix قصد دارد SSDهای مشتری و سازمانی را به طور متوالی در بازار محصولات خود گسترش دهد.

با افزایش تعداد لایهها در NAND flash، کاهش جریان سلول، جفت شدن (پیچ خوردگی) حفره کانال و خراب شدن توزیع سلول به دلیل عدم تطابق مضاعف پشته رخ میدهد. SK Hynix با اتخاذ فن آوریهای نوآورانه مانند کاهش ارتفاع لایه سلول، کنترل زمان متغیر لایه و ترازبندی فوقالعاده دقیق، این چالشها را پشت سر گذاشته و حافظه NAND Flash با 176 لایه برتر صنعت را توسعه داده است.

این شرکت همچنین قصد دارد با گسترش محصولات 1TB با دو برابر کردن تراکم محصولات مبتنی بر NAND Flash با 176 لایه رقابت خود را در تجارت حافظه فلش NAND افزایش دهد.

Jung Dal Choi، رئیس توسعه NAND flash در SK hynix، گفت: "صنایع NAND flash در تلاشند تا همزمان فن آوریهای یکپارچه سازی بالا و حداکثر بهرهوری را بهبود بخشند. SK hynix به عنوان پیشگام 4D NAND، بازار NAND flash را با بالاترین بهرهوری و فناوری در صنعت هدایت خواهد کرد." طبق گفته ارائه دهنده اطلاعات بازار Omdia، انتظار میرود بازار حافظه NAND flash از 8/431 میلیارد گیگابایت در سال 2020 به 1.366 تریلیون گیگابایت در سال 2024 با نرخ رشد سالانه مرکب (CAGR) 33.4 درصد گسترش یابد.

4D NAND

SK hynix نام آن را '4D NAND Flash' گذاشت و در سال 2018 با ترکیب ساختار سلول CTF و فناوری PUC حافظه NAND Flash با 96 لایه تمایزی که همزمان در عملکرد و بهرهوری به دست آورد را برجسته کند.

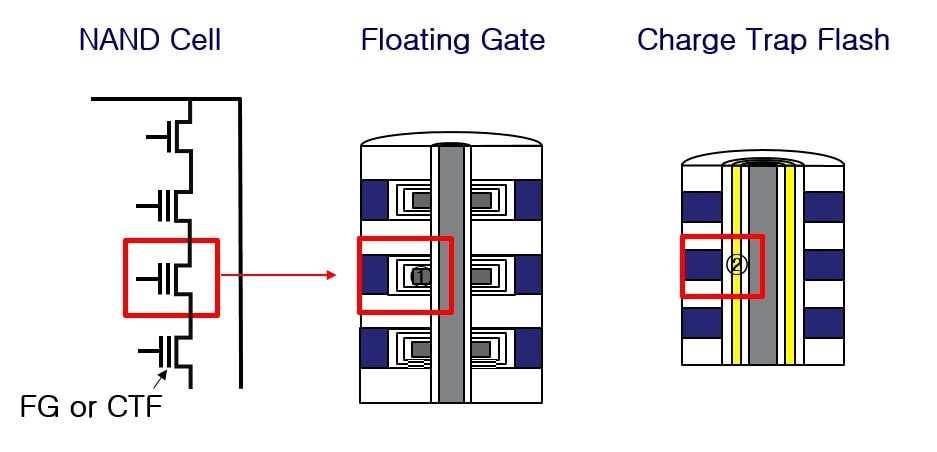

(CTF) Charge Trap Flash

بر خلاف گیت شناور، که بارهای الکتریکی را در هادیها ذخیره میکند، CTF بارهای الکتریکی را در غیرهادیها ذخیره میکند، که این امر تداخل بین سلولها را از بین میبرد، عملکرد خواندن و نوشتن را بهبود میبخشد در حالی که مساحت سلول را در واحد کاهش میدهد. اکثر شرکتهای 3D NAND از CTF استفاده میکنند.

PUC (Peri. Under Cell)

فناوری که با قرار دادن مدارهای محیطی در زیر آرایه سلول، بهرهوری تولید را به حداکثر میرساند.

انتخاب فناوری آرایه سلول دو بخشی

Word line ولتاژ را به سلولهای موجود در مدار NAND flash اعمال میکند. هر چه تعداد لایهها بیشتر باشد، Word line نازکتر شده، که این امر باعث کاهش ارتفاع سلول میشود و همچنین مقاومت بیشتری که بر روی Word line ایجاد میشود سرعت را تحت تأثیر قرار میدهد. با تقسیم سلول متصل به Word line به دو سلول، میتوان مقاومت را کاهش داد، در نتیجه زمان استفاده از ولتاژ را کاهش میدهد و سرعت خواندن را بهبود میبخشد.

فناوری کاهش ارتفاع بین لایهای

با افزایش تعداد لایهها، ایجاد حفره برای تشکیل سلولها دشوار میشود. این امر منجر به افزایش مقاومت و کاهش جریان میشود و عملکرد بالا و قابلیت اطمینان را دشوار میکند. به همین دلیل باید تا آنجا که ممکن است از ارتفاع بین لایههای سلول کاسته شود، اما این امر باعث افزایش تداخل و میزان نقص بین سلولها میشود. فناوری کاهش ارتفاع بین لایههای سلول نه تنها ارتفاع لایههای سلول 176 لایه را به طور چشمگیری کاهش میدهد، بلکه از طریق فرآیندهای مرتبط و تکنیکهای طراحی، عملکرد/قابلیت اطمینان را نیز تضمین میکند.

فناوری کنترل زمان متغیر لایه

افزایش تعداد لایهها و کاهش ارتفاع لایه اغلب منجر به مخدوش شدن حفره کانال و خراب شدن پراکندگی سلول میشود که عملکرد و قابلیت اطمینان هر لایه را کاهش میدهد. این فناوری مقدار و زمان ولتاژ اعمال شده را با توجه به مشخصات هر لایه تنظیم میکند تا ویژگیهای سلول را ثابت نگهدارد و عملکرد و قابلیت اطمینان را بهبود بخشد.

فناوری هم ترازی بسیار دقیق

این صنایع از فرآیند دو پشتهای که حفرهها را دو برابر میکند، استفاده میکنند. زیرا با افزایش تعداد لایهها، ایجاد حفره برای تشکیل سلول یکباره امکانپذیر نیست. به حداقل رساندن ناهماهنگی دو پشته، هسته اصلی این فناوری است. اگر پشتهها به درستی تراز نشوند، منجربه جریان ضعیف بین پشتهها و بروز خرابی، کاهش سرعت عملکرد و قابلیت اطمینان میشود. SK hynix از زمان تولید محصول 72 لایه در سال 2017، از فناوری دو پشتهای در محصول 176 لایه استفاده کرده که این فناوری به صورت خودکار مکان و اندازه حفرهها را بر اساس دانش فنی خود تصحیح میکند.